# Clock Synchronization, IEEE 1588 and Cyber-Physical Systems

John C. Eidson

University of California at Berkeley eidson@eecs.berkeley.edu

Dreams seminar, UC Berkeley November 14, 2011

#### Outline

- CPS background

- Timing, clocks, and IEEE 1588

- Sources of synchronization error

- Uses of IEEE 1588 in CPS

- Future

# Controlling a CPS, e.g. industrial automation Learning about a CPS, e.g. test & measurement

Cyber-Physical System (CPS)

Cyber World (computers and networks) Computation, Control, Communication (CONTROL: based on a model of the physical world) (LEARNING: building a model of the physical world)

Physical World Natural world: physics, chemistry, ecology, biology · · · Man-made world: airplane, power grid, internet, printing press, automobile,  $iPod, \cdots ad$ infinitum

Both timing and value are important in a CPS!

Control

Courtesy of Bosch-Rexroth

Measurement

Courtesy of Brüel & Kjær

Trend: More transducers, distributed systems => synchronized clocks

- IEEE 1588 exists due to industry's:

- Increasing requirement for <u>distributed systems</u>

- Customer demand for <u>standards based</u> solutions

- Move to Ethernet from proprietary networks for perceived cost reasons

- Need for timing <u>accuracy better than 1 µs</u>

- Nothing profound or magical about 1588 just the right thing at the right time

- But it did help focus the discussion on timing in distributed Ethernet-based systems!

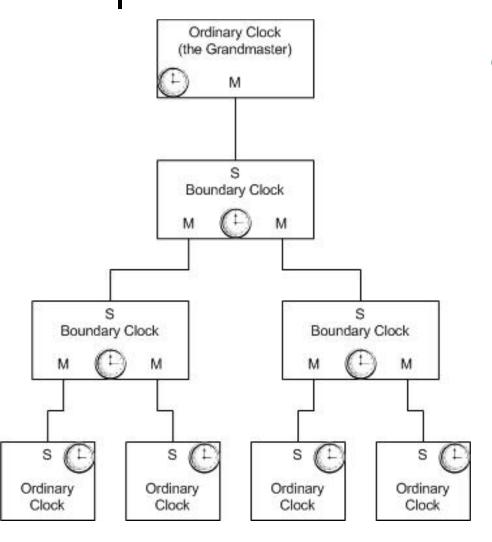

### Master-slave hierarchy of ordinary and boundary clocks

- Hierarchy based on pair-wise comparison of:

- 1. priority-1

- class (UTC traceability)

- accuracy (with respect to UTC)

- 4. variance

- 5. priority-2

- 6. UUID (tiebreaker)

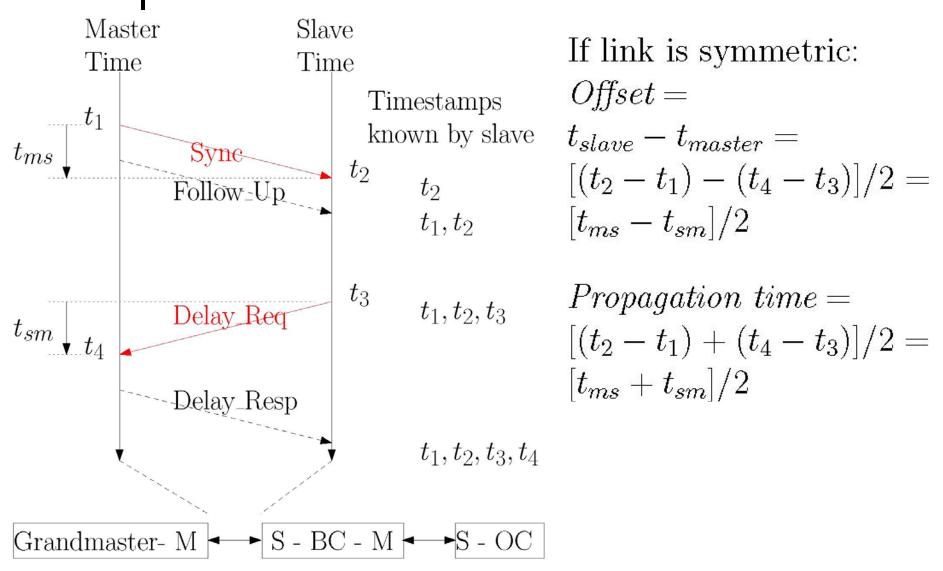

### Synchronization: delay request-response mechanism

- If the link is not symmetric

- The propagation time is the mean of the master-to-slave and slave-to-master propagation times

- The offset is in error by the difference between the actual master-to-slave and mean propagation times

- IF you know the asymmetry, the standard specifies how to correct for it

- Correcting asymmetry is a major concern in high accuracy synchronization. This is true for all twoway synchronization protocols and is not unique to 1588.

#### Sources of synchronization error

John C. Eidson, UC Berkeley

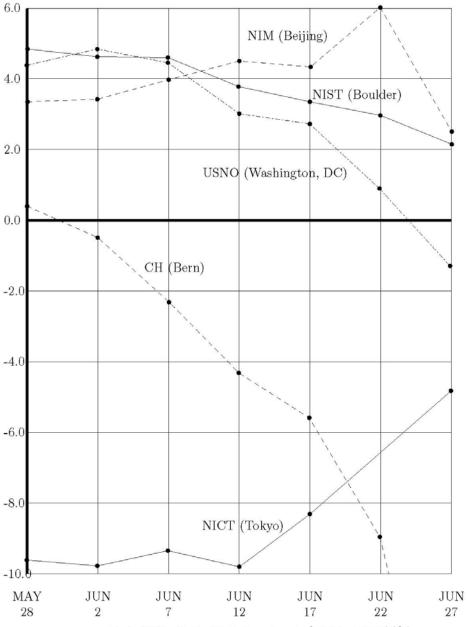

#### UTC<sub>i</sub> vs. UTC

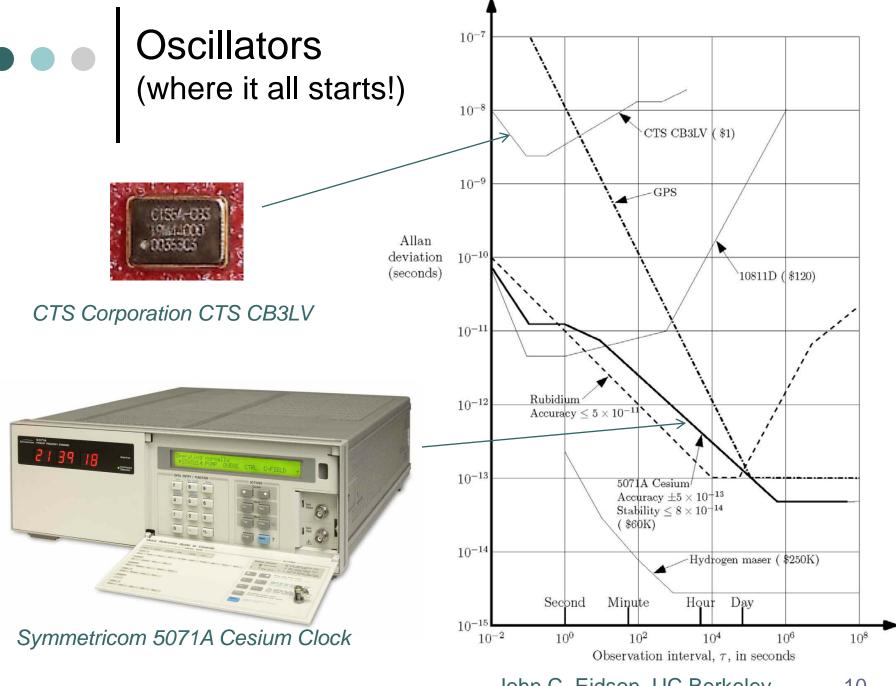

Even atomic clocks drift! Keeping precise and accurate time is very difficult.

Date 2011, 0h UTC: Laboratory k [UTC - UTC(k)]/ns BUREAU INTERNATIONAL DES POIDS ET MESURES CIRCULAR T 282 2011 JULY 07, 09h UTC

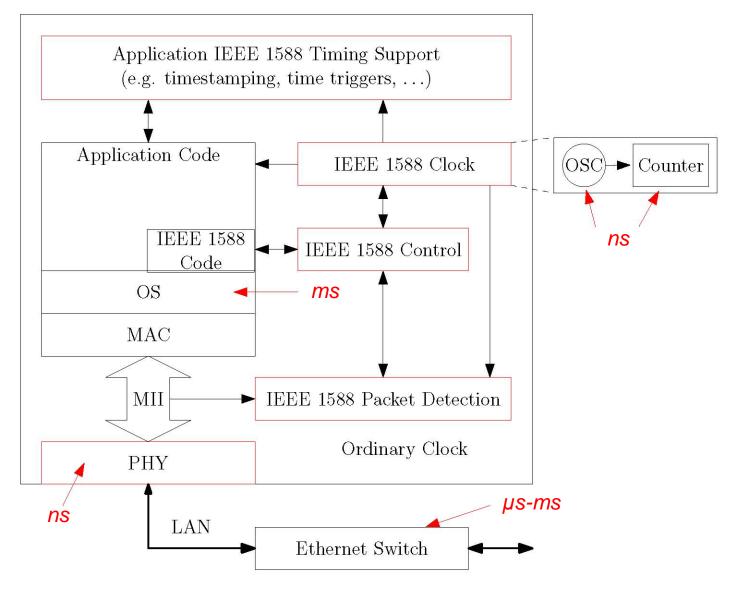

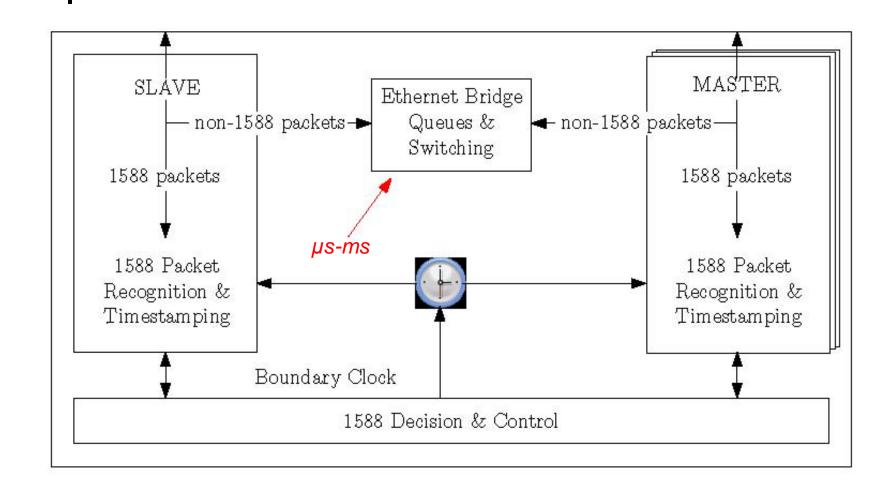

#### IEEE1588 Boundary Clock

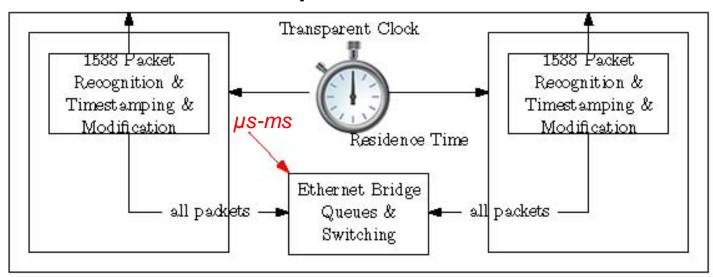

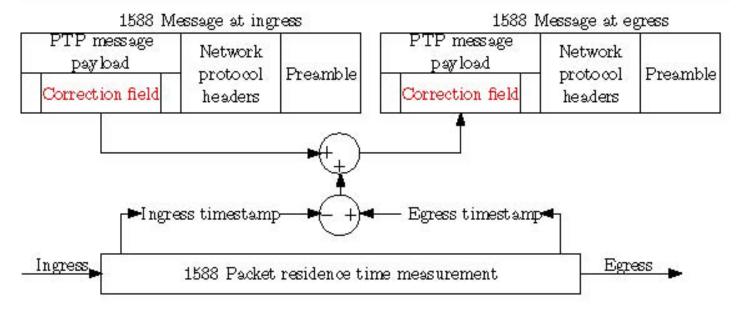

#### IEEE 1588 Transparent Clock

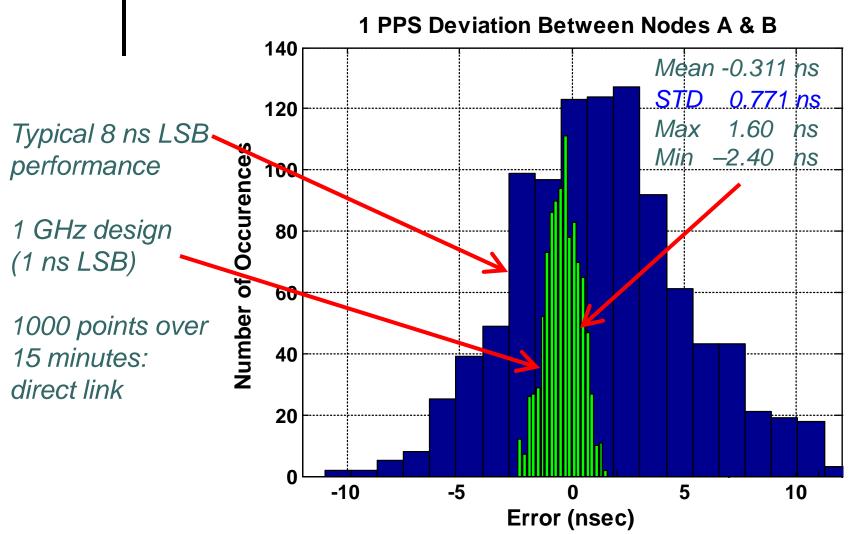

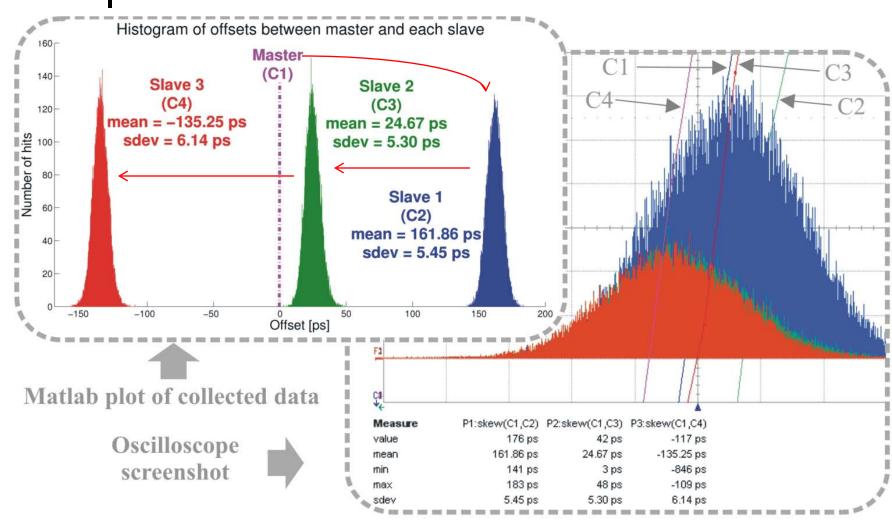

#### How well can you synchronize?

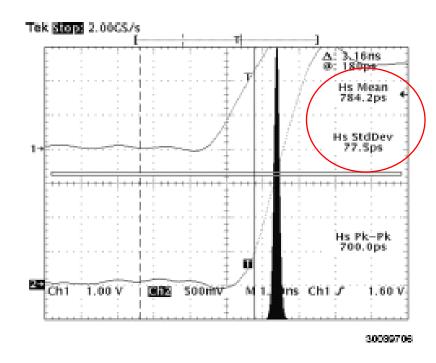

From: Update on High Precision Time Synchronization, Vook, et.al., IEEE-1588 Conference, Zurich, October 2005

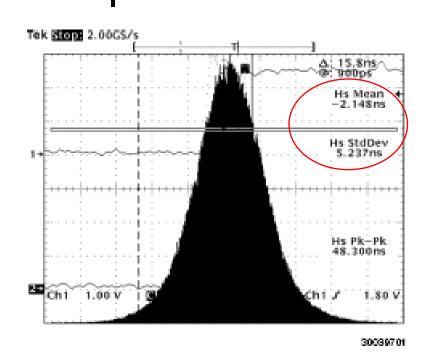

#### IEEE 1588v2/PTP and SyncE/ITU-T G.8261

FIGURE 7. Master to Slave 10 MHz CLK\_OUT FIGURE 10. Master to Slave 10 MHz CLK\_OUT

Synchronization with Synchronous Ethernet Mode Synchronization with Synchronous Mode Enabled and

Disabled Crystal Slave Reference Clock

From: "DP83640 Synchronous Ethernet Mode: Achieving Sub-nanosecond Accuracy in PTP Applications, National Semiconductor Application Note 1730, David Miller, September 2007

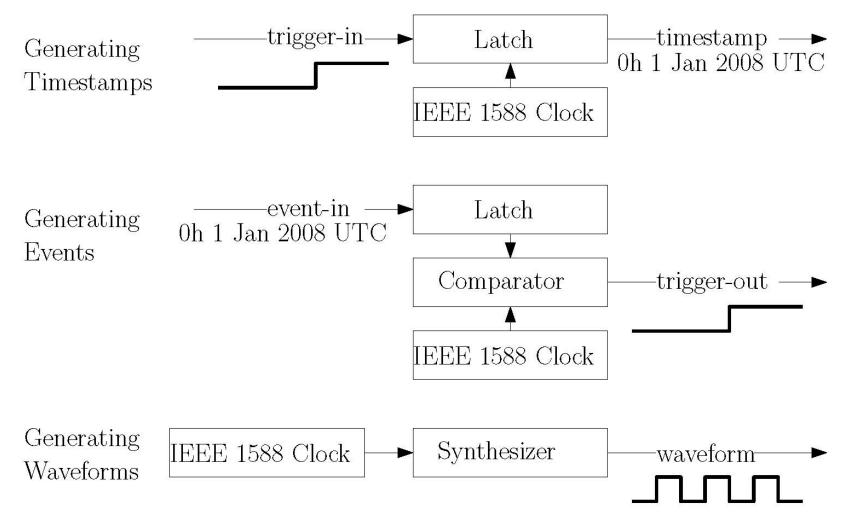

#### How do you use a synchronized clock?

(all 3 forms supported in DP83640 PHY chip)

### IEEE 1588 Commercial products (partial listing)

- Boundary and transparent clocks: Hirschmann, RuggedCom, Cisco, Siemens, Huawei,...

- PHY chips: National Semiconductor, Intel, Zarlink, Vitesse, Broadcom, Marvell,...

- Microprocessors: Intel, Conemtech AB, Analog Devices, Freescale,...

- Protocol stacks: IXXAT, RTS, Flexibilis,...

- FPGA IP Blocks: System-on-chip Engineering, MoreThanIP, Xilinx, Altera,...

- Ordinary clocks: Symmetricom, Meinberg, ...

- Debug help: Wireshark, Ixia, Symmetricom,...

- ISPCS- IEEE International Symposium on Precision Clock Synchronization

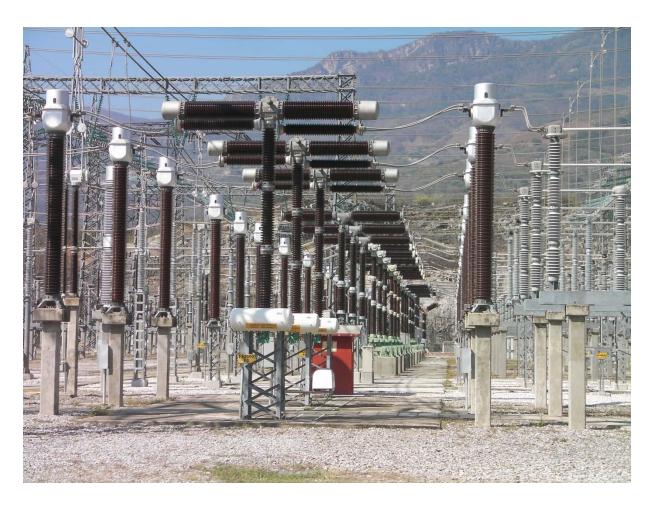

#### Power system applications

GE uses 1588 in the Mark<sup>™</sup>VIe control system for large generators, turbines, wind farms, and other DCS applications. (>50K I/O Packs with 1588 shipped to date)

Courtesy of General Electric

#### Power system synchrophasor application

Photo courtesy of Veselin Skendzic

#### Power system synchrophasor application

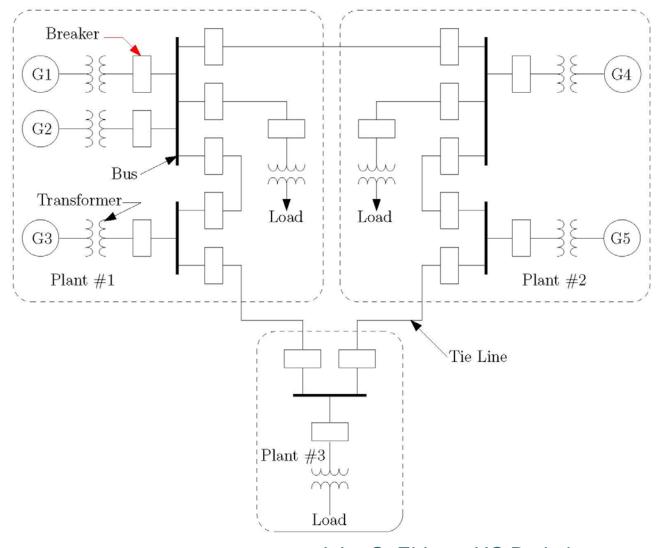

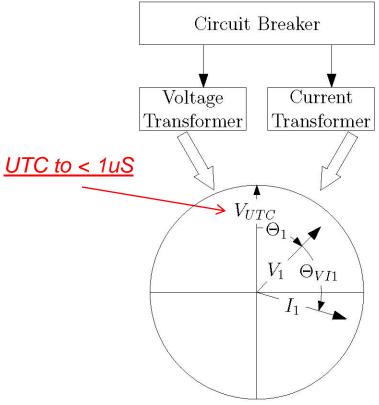

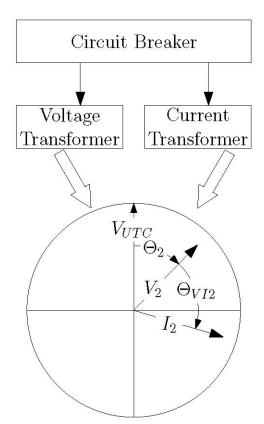

#### Power system synchrophasors

IEEE 1588 referenced in C37.238, C38.118.1 and C37.118.2

Synchrophasor data:  $\Theta_1$ ,  $V_1$ ,  $I_1$ ,  $\Theta_{VI1}$ Power factor:  $\cos(\Theta_{VI1})$

Synchrophasor data:  $\Theta_2$ ,  $V_2$ ,  $I_2$ ,  $\Theta_{VI2}$ Power factor:  $\cos(\Theta_{VI2})$

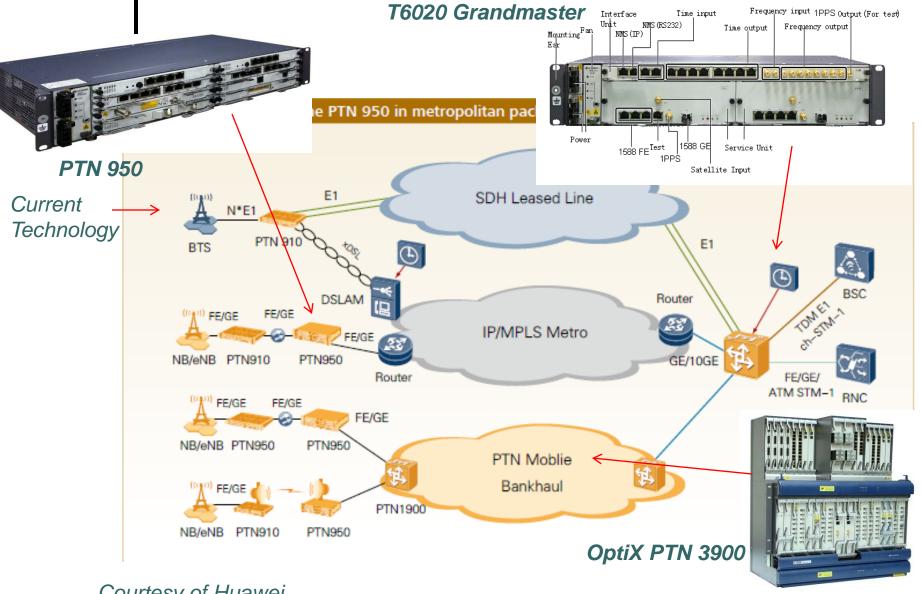

#### Telecommunications applications

- Cellular backhaul, pico and femto cells are the first major telecommunications applications

- Femto cell access points: ~4M in 2011 to 48M in 2014 (from 'Femtocell Market Status' – Informa, a white paper of the femtoforum)

- IEEE 1588 enabled PHY chips appearing, e.g. Broadcom BCM54682E — octal-port QSGMII 10/100/1000BASE-T GbE transceiver

# Standardization activity for packet-based time and frequency transfer in telecommunications

- ITU-T SG15 Q13

- ITU-T Recommendation G.8265.1 (10/2010), Precision Time Protocol Profile for Frequency Synchronization

- Starting G.8275 and G.8275.1 for time/phase transfer using IEEE 1588

- o IETF: 'Tic-Tock'

- ICAP- IEEE 1588 Conformity Alliance (testing & certification)

## Synchronization requirements for wireless air interface technologies

| Technology               | Frequency Accuracy | Phase Accuracy                                              |

|--------------------------|--------------------|-------------------------------------------------------------|

| GSM (2G)                 | ±50 ppb            | Not required                                                |

| UMTS                     | ±50 ppb            | Not required                                                |

| CDMA 2000                | ±50 ppb            | ±3.0 µs                                                     |

| WCDMA                    | ±50 ppb            | ±1.25 μs reference to BTS<br>±2.55 μs between base stations |

| Pico RBS (WCDMA and GSM) | ±100 ppb           | ±3.0 µs                                                     |

Based on a Juniper Networks white paper- 'Synchronization Deployment Considerations for IP RAN Backhaul Operators'

#### Typical cellular backhaul architecture

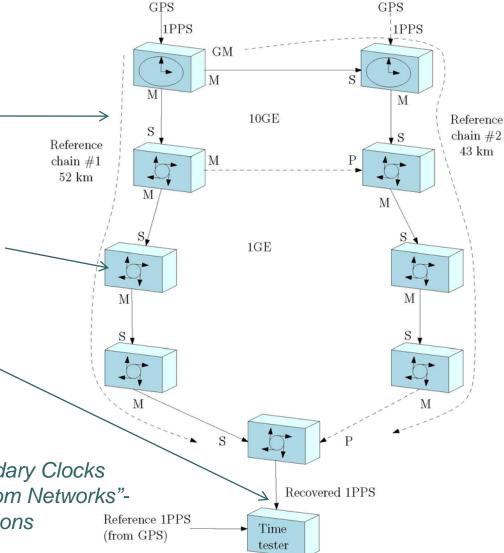

#### Telecom time transfer field trial in China

Each chain had 15 boundary clocks

BCs used SyncE for frequency and 1588 for time transfer

Accumulated error

< 3 µs requirement for TD-SCDMA

From "Using IEEE 1588 and Boundary Clocks for Clock Synchronization in Telecom Networks"-Ouellette, et.al. IEEE Communications

Refer (from Magazine • February 2011

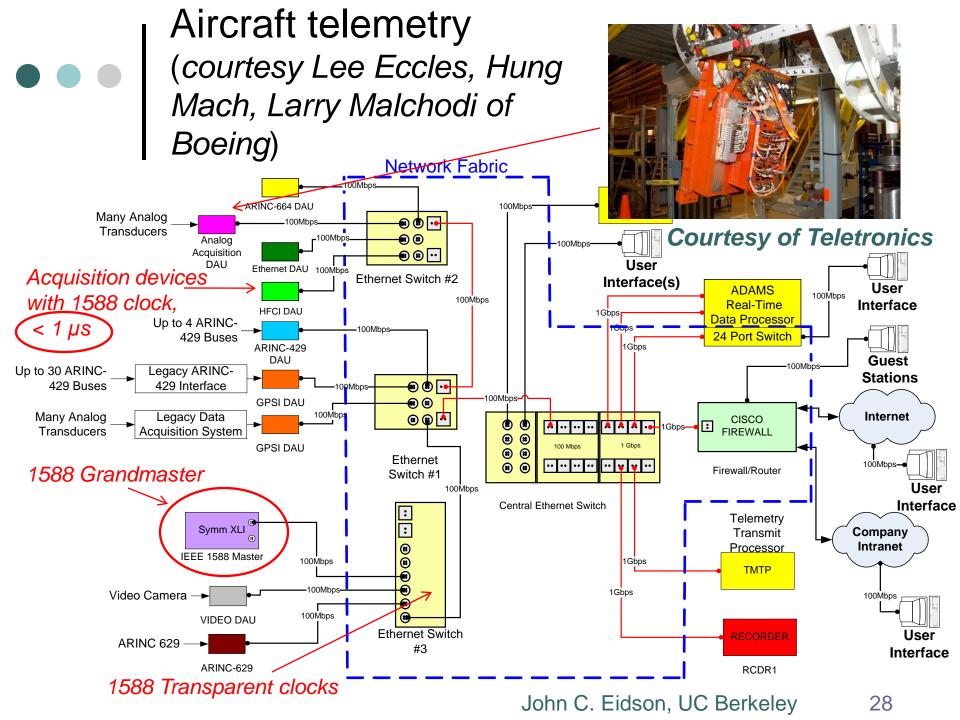

#### Industrial automation example

- Rockwell Ethernet/IP<sup>tm</sup>

Time-based control over

Ethernet

- Commands and sensor readings are locally timestamped

- Has been installed on 130 axis packaging machines

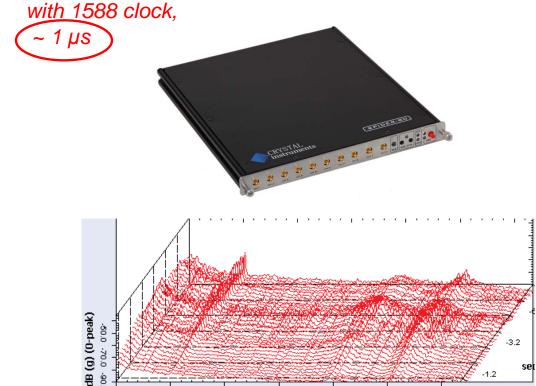

### Sound, vibration,..., machine condition monitoring

Acquisition devices

Courtesy Brüel & Kjaer

Photograph by Alan D. Monyelle, USN, 5/23/02

Courtesy Crystal Instruments

Frequency (Hz)

26000.0

31000.0

6000.0

11000.0

#### **CERN's White Rabbit Project**

(based on "White Rabbit: a PTP Application for Robust Sub-nanosecond Synchronization"- Maciej Lipinski, et.al., ISPCS 2011 Munich)

- Goal: Develop an alternate timing and control system for the General Machine Timing at CERN

- Synchronization of up to 2000 nodes with subnanosecond accuracy, an upper bound on frame delivery and a very low data loss rate

- Based on and compatible with Ethernet (IEEE 802.3), Synchronous Ethernet (ITU-T Std. G.8262, 2007) and IEEE 1588-2008.

- For sub-nanosecond EVERYTHING matters: oscillators; media, PHY, board asymmetry, temperature, ...

#### White Rabbit Performance: Sub-nanosecond synchronization error over three 5km fiber optic links!

## What does the future hold for timing and CPS?

Advances in clock physics

- Symmetricom SA.45s CSAC

- Innovations in time and synchronization in CPS applications, e.g. IA, telecom

- Evolution of applicable standards

- IEEE 802 community takes timing seriously

- Advances in time specific programming languages and development environments: example- the <u>UC Berkeley Ptides Project</u>

## Using clocks- UC Berkeley Ptides Project (Patricia Derler, John Eidson, Slobodan Matic, Prof. Edward Lee, Michael Zimmer)

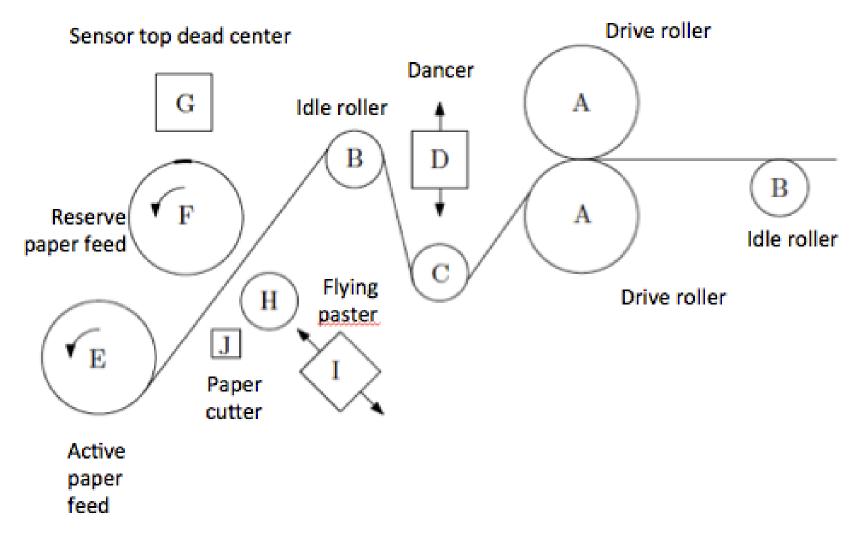

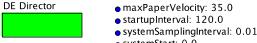

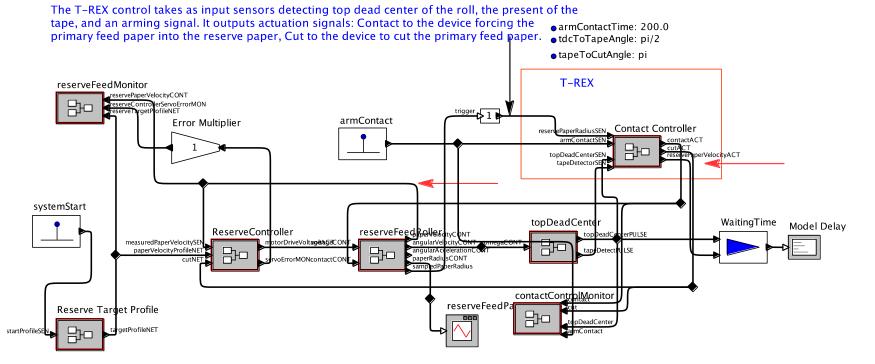

#### System model

- coreRadius: 0.07 o fullRollRadius: 0.7

- paperThickness: 0.000075 systemStart: 0.0

This design consists of a model of a controler (T-REX) and a plant mode (the rest of the design. The plant models the dynamics of a DC motors driving a feed roller and a controler to cause the resulting paper velocity to track the input profile. All of this is a subset of the larger printing press model.

#### T-REX Controller

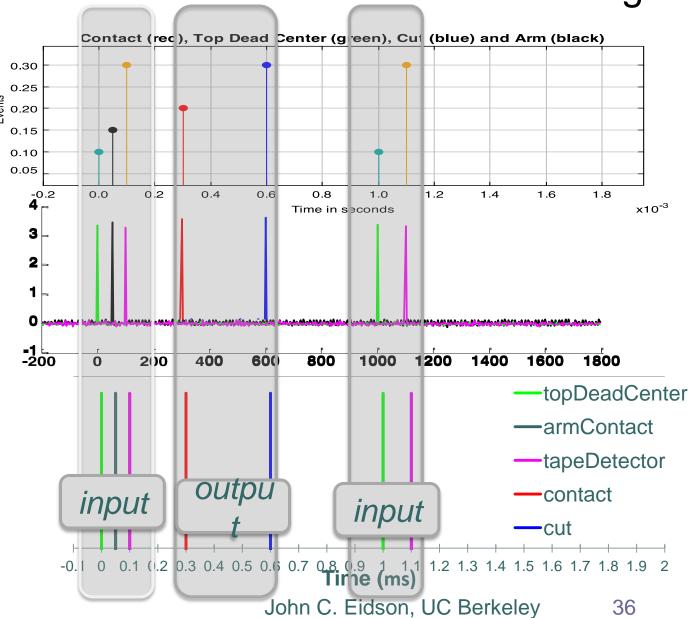

#### Renesas vs. XMOS: Measured I/O timing

Simulation

Renesas

**XMOS**